En 1965, Gordon Moore, cofundador de Intel, formuló lo que se convertiría en la "Ley de Moore". Durante más de medio siglo, esta ley respaldó las constantes mejoras en el rendimiento de los circuitos integrados (CI) y la disminución de los costos, la base de la tecnología digital moderna. En resumen: el número de transistores en un chip prácticamente se duplica cada dos años.

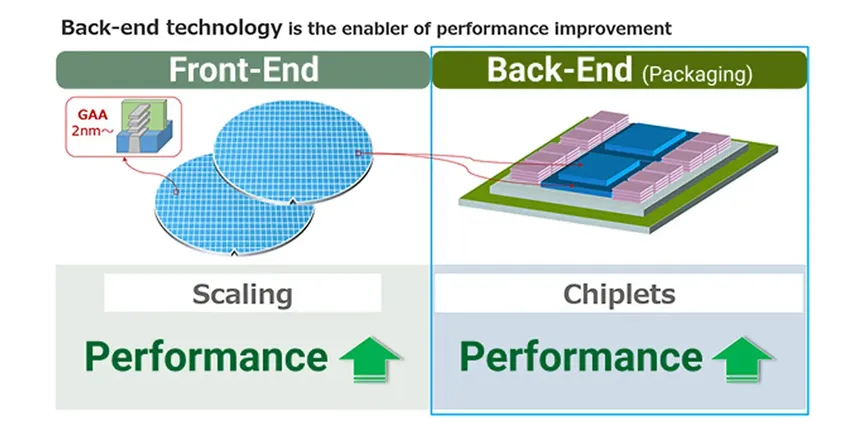

Durante años, el progreso siguió ese ritmo. Ahora, el panorama está cambiando. Una mayor contracción se ha vuelto difícil; los tamaños de las características se han reducido a tan solo unos pocos nanómetros. Los ingenieros se enfrentan a límites físicos, pasos de proceso más complejos y costos crecientes. Las geometrías más pequeñas también reducen el rendimiento, lo que dificulta la producción a gran escala. Construir y operar una fábrica de vanguardia requiere un capital y una experiencia ingentes. Por lo tanto, muchos argumentan que la Ley de Moore está perdiendo fuerza.

Ese cambio ha abierto la puerta a un nuevo enfoque: los chiplets.

Un chiplet es una pequeña matriz que realiza una función específica; básicamente, es una porción de lo que solía ser un chip monolítico. Al integrar varios chiplets en un solo encapsulado, los fabricantes pueden ensamblar un sistema completo.

En la era monolítica, todas las funciones residían en un gran chip, por lo que un defecto en cualquier lugar podía destruir todo el chip. Con los chiplets, los sistemas se construyen a partir de un chip "conocido en buen estado" (KGD), lo que mejora drásticamente el rendimiento y la eficiencia de fabricación.

La integración heterogénea (combinando matrices construidas en diferentes nodos de proceso y para distintas funciones) hace que los chiplets sean especialmente potentes. Los bloques de cómputo de alto rendimiento pueden usar los nodos más recientes, mientras que la memoria y los circuitos analógicos se mantienen en tecnologías maduras y rentables. El resultado: mayor rendimiento a menor costo.

La industria automotriz está particularmente interesada. Los principales fabricantes de automóviles están utilizando estas técnicas para desarrollar futuros SoCs para vehículos, con una adopción masiva prevista para después de 2030. Los chiplets les permiten escalar la IA y los gráficos de forma más eficiente, a la vez que mejoran el rendimiento, lo que optimiza tanto el rendimiento como la funcionalidad de los semiconductores automotrices.

Algunas piezas de automóviles deben cumplir estrictos estándares de seguridad funcional y, por lo tanto, dependen de nodos más antiguos y probados. Mientras tanto, los sistemas modernos, como los sistemas avanzados de asistencia al conductor (ADAS) y los vehículos definidos por software (SDV), requieren mucha más capacidad de procesamiento. Los chiplets cubren esa brecha: al combinar microcontroladores de seguridad, gran capacidad de memoria y potentes aceleradores de IA, los fabricantes pueden adaptar los SoC a las necesidades de cada fabricante de automóviles con mayor rapidez.

Estas ventajas van más allá del sector automovilístico. Las arquitecturas chiplet se están extendiendo a la IA, las telecomunicaciones y otros ámbitos, acelerando la innovación en diversas industrias y convirtiéndose rápidamente en un pilar de la hoja de ruta de los semiconductores.

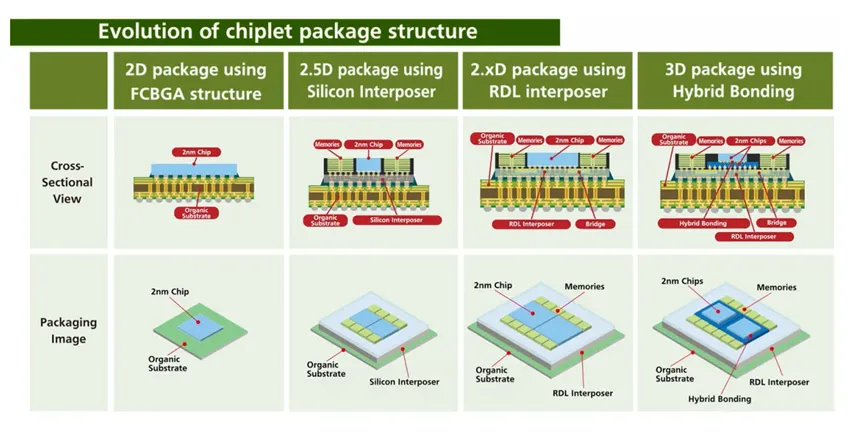

La integración de chiplets depende de conexiones entre matrices compactas y de alta velocidad. El elemento clave es el intercalador: una capa intermedia, generalmente de silicio, debajo de las matrices que enruta las señales de forma similar a una pequeña placa de circuito. Unos mejores intercaladores implican un acoplamiento más estrecho y un intercambio de señales más rápido.

El encapsulado avanzado también mejora el suministro de energía. Las densas matrices de diminutas conexiones metálicas entre matrices proporcionan amplios caminos para la corriente y los datos incluso en espacios reducidos, lo que permite una transferencia de gran ancho de banda y un uso eficiente del área limitada del encapsulado.

El enfoque predominante hoy en día es la integración 2.5D: colocar múltiples matrices una junto a la otra en un intercalador. El siguiente paso es la integración 3D, que apila las matrices verticalmente mediante vías a través del silicio (TSV) para lograr una densidad aún mayor.

La combinación del diseño modular de chips (que separa funciones y tipos de circuitos) con el apilamiento 3D produce semiconductores más rápidos, más pequeños y con mayor eficiencia energética. La ubicación conjunta de memoria y computación proporciona un gran ancho de banda para grandes conjuntos de datos, ideal para IA y otras cargas de trabajo de alto rendimiento.

Sin embargo, el apilamiento vertical presenta desafíos. El calor se acumula con mayor facilidad, lo que complica la gestión térmica y el rendimiento. Para abordar esto, los investigadores están desarrollando nuevos métodos de empaquetado que gestionen mejor las restricciones térmicas. Aun así, el impulso es fuerte: la convergencia de chiplets y la integración 3D se considera ampliamente un paradigma disruptivo, listo para tomar la posta donde la Ley de Moore se queda atrás.

Hora de publicación: 15 de octubre de 2025